### Datasheet

DS001066

# Mira050

### 1/7" Compact 0.5 MP NIR Enhanced Global Shutter Image

v1-01 • 2023-Feb-20

7

### **Content Guide**

| 1 | General Description                      | 5 |

|---|------------------------------------------|---|

| 2 | Specifications and Special<br>Features 4 | ŀ |

| 3 | Applications6                            | 5 |

| 4 | Block Diagram 7                          | , |

| 5 | Ordering Information 8                   | 3 |

| 6 | Revision Information                     | ) |

Legal Information......10

### **1** General Description

Mira050 is a compact 0.5 MP Near IR enhanced global shutter image sensor designed for 2D and 3D consumer and industrial machine vision applications. The sensor has a small 2.79 µm pixel size with high sensitivity made possible by a state of the art BSI technology. The sensor has a MIPI CSI-2 interface to allow easy interfacing with a plethora of processors and FPGAs. Due to its small size, configurability and high sensitivity both in visual as well as NIR, the Mira050 is well suited for 2D and 3D applications, which include Active Stereo Vision, Structured Light Vision and AR/VR. High sensitivity in NIR enables increased measurement range and allows overall system power consumption optimization which is key for battery powered consumer and industrial applications.

## **2** Specifications and Special Features

#### Figure 1:

**Typical Specifications Mira050**

| Parameter                                                             | Value                                               | Remark                                                                                                    |  |

|-----------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Active Pixels                                                         | 576 (H) x 768 (V) CSP<br>600 (H) x 800 (V) Bare Die | On CSP the addressable area is 600 x 800 but only 576 x 768 is useable.                                   |  |

| Pixel                                                                 | 2.79 μm × 2.79 μm                                   | BSI stacked technology with high NIR sensitivity. Low noise and low cross talk.                           |  |

| Optical Format                                                        | 1/7"                                                |                                                                                                           |  |

| Dimensions                                                            | 2.25 mm x 2.75 mm – Die<br>2.29 mm x 2.83 mm – CSP  | Active area 60% of total                                                                                  |  |

| Shutter Type                                                          | Voltage domain pipelined global shutter             | Possibility of exposure of next image during readout of the previous image.                               |  |

| Quantum Efficiency (QE)                                               | 94 / 56 / 36 %                                      | 550 / 850 / 940 nm Mono                                                                                   |  |

| Supported Lens Chief Ray<br>Angle (CRA)                               | 0° to 30°                                           | Extra wide acceptance angle of the Mira050 pi<br>means any lens profile with these CRA values<br>be used. |  |

| ADC Modes                                                             | 8-bit   10-bit   10-bit HS   12-bit                 |                                                                                                           |  |

| Max Frames Per Second Full<br>Resolution                              | 120 fps                                             | All ADC modes                                                                                             |  |

|                                                                       | $1x \rightarrow 4x$ step: $2x$                      | 12-bit   10-bit HS (Default mode)                                                                         |  |

|                                                                       | $1x \rightarrow 16x$ step: $2x$                     | 10-bit (Default mode)                                                                                     |  |

| Analog Gain                                                           | $1x \rightarrow 4x$ step: 3%                        | 10-bit HS (Fine gain mode)                                                                                |  |

|                                                                       | $1x \rightarrow 32x$ step: $2x$                     | 8-bit (Default mode)                                                                                      |  |

|                                                                       | $1x \rightarrow 16x$ step: 3%                       | 8-bit (Fine gain mode)                                                                                    |  |

| Digital Gain                                                          | $1x \rightarrow 16x$ step: 1/16x                    | 8-bit  10-bit   10-bit HS   12-bit                                                                        |  |

| Data Interface MIPI CSI-2 v1.3 DPHY v1.2   1 Data lane   1 Clock lane |                                                     | 1.5 Gbps with data scrambling support                                                                     |  |

#### Figure 2:

**Special Features**

| Features                                | Benefits                                                                                                                                               |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable registers                  | Programming of window coordinates, timing parameters, exposure time, mirror, flipping, cropping.                                                       |

| High sensitivity and NIR enhanced pixel | High sensitivity and compact pixel size achieved via state of the art BSI technology with NIR enhancement resulting in less power hungry illuminators. |

| Context switching                       | Two register contexts for on the fly configuration changes.                                                                                            |

|                                         | Defect pixel detection and correction.                                                                                                                 |

|                                         | Image statistics generation.                                                                                                                           |

|                                         | Event detection.                                                                                                                                       |

| On-chip processing                      | In pixel Background light cancellation.                                                                                                                |

|                                         | Digital Pixel Binning.                                                                                                                                 |

|                                         | Black Sun Protection.                                                                                                                                  |

|                                         | Flexible ROI selection.                                                                                                                                |

| On-chip advanced power management       | Smart powering of on-chip blocks with respect to frame rate and exposure time resulting in extended battery life.                                      |

| On-chip temperature sensor              | Accurate temperature reading on junction temperature.                                                                                                  |

| Illumination synchronization trigger    | Accurate timing between illumination and actual exposure.                                                                                              |

## **3** Applications

- Facial Authentication for mobile devices and points of payments

- Active Stereo and Structured Light Vision (Robotics and other applications)

- Eye, head, hand, environment tracking for AR/VR

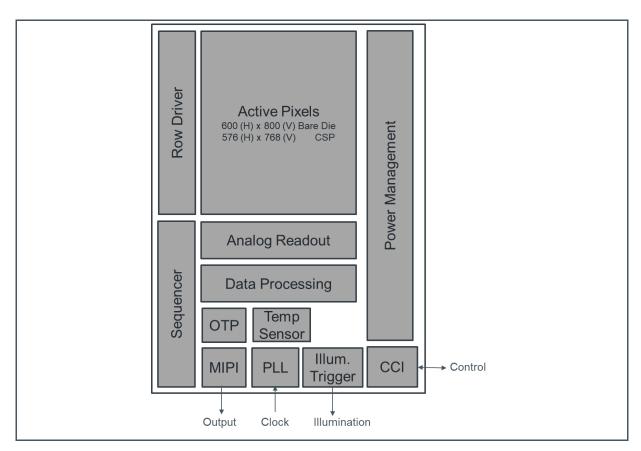

### 4 Block Diagram

#### Figure 3:

**Functional Blocks of Mira050**

# 5 Ordering Information

| Product Code   | Ordering Code            | Package                           | Delivery Form | Delivery<br>Quantity |

|----------------|--------------------------|-----------------------------------|---------------|----------------------|

| Mira050-1QM1D0 | 511930021<br>Q65113A5663 | Reconstructed<br>Wafer (bare die) | R/W           | Multiples of 3418    |

| Mira050-1QM1WB | 511930019<br>Q65113A5422 | CSP                               | Tray          | Multiples of 120     |

### 6 **Revision Information**

| Changes from previous version to current revision v1-01 | Page |  |  |

|---------------------------------------------------------|------|--|--|

| Initial short datasheet                                 |      |  |  |

| Removed "Remarks" for "ADC Modes" under Figure 1        | 4    |  |  |

• Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

Correction of typographical errors is not explicitly mentioned.